- 您现在的位置:买卖IC网 > Sheet目录309 > ADZS-BF561-EZLITE (Analog Devices Inc)BOARD EVAL ADSP-BF561

�� �

�

�

�ADSP-BF561 �

�Serial� Ports�

��through� Figure� 22� on� Page� 34� describe� Serial� Port� operations.�

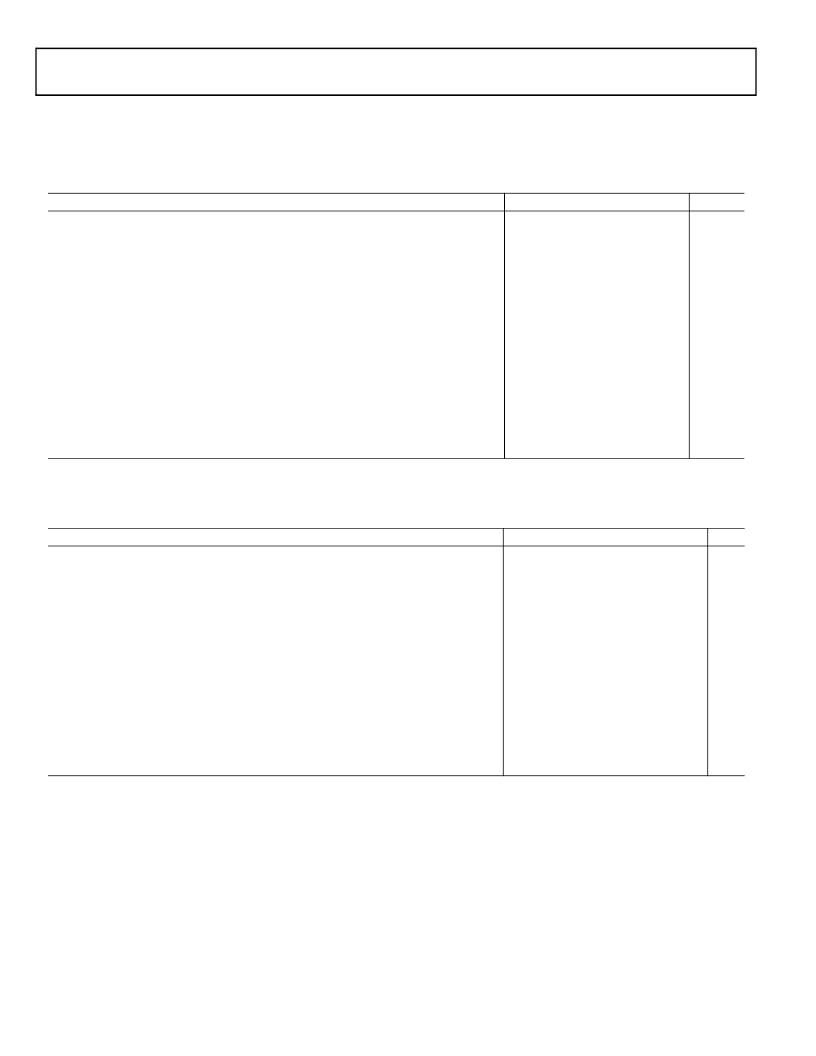

�Table� 23.� Serial� Ports—External� Clock�

�Parameter�

�Min�

�Max�

�Unit�

�Timing� Requirements�

�t� SFSE�

�t� HFSE�

�t� SDRE�

�t� HDRE�

�t� SCLKW�

�t� SCLK�

�t� SUDTE�

�t� SUDRE�

�TFSx/RFSx� Setup� Before� TSCLKx/RSCLKx� 1�

�TFSx/RFSx� Hold� After� TSCLKx/RSCLKx� 1�

�Receive� Data� Setup� Before� RSCLKx� 1�

�Receive� Data� Hold� After� RSCLKx� 1�

�TSCLKx/RSCLKx� Width�

�TSCLKx/RSCLKx� Period�

�Start-Up� Delay� From� SPORT� Enable� To� First� External� TFSx�

�Start-Up� Delay� From� SPORT� Enable� To� First� External� RFSx�

�3.0�

�3.0�

�3.0�

�3.0�

�4.5�

�15.0�

�4.0�

�4.0�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�TSCLKx�

�RSCLKx�

�Switching� Characteristics�

�t� DFSE�

�t� HOFSE�

�t� DDTE�

�t� HDTE�

�TFSx/RFSx� Delay� After� TSCLKx/RSCLKx� (Internally� Generated� TFSx/RFSx)� 2�

�TFSx/RFSx� Hold� After� TSCLKx/RSCLKx� (Internally� Generated� TFSx/RFSx)� 2�

�Transmit� Data� Delay� After� TSCLKx� 2�

�Transmit� Data� Hold� After� TSCLKx� 2�

�0.0�

�0.0�

�10.0�

�10.0�

�ns�

�ns�

�ns�

�ns�

�1�

�2�

�Referenced� to� sample� edge.�

�Referenced� to� drive� edge.�

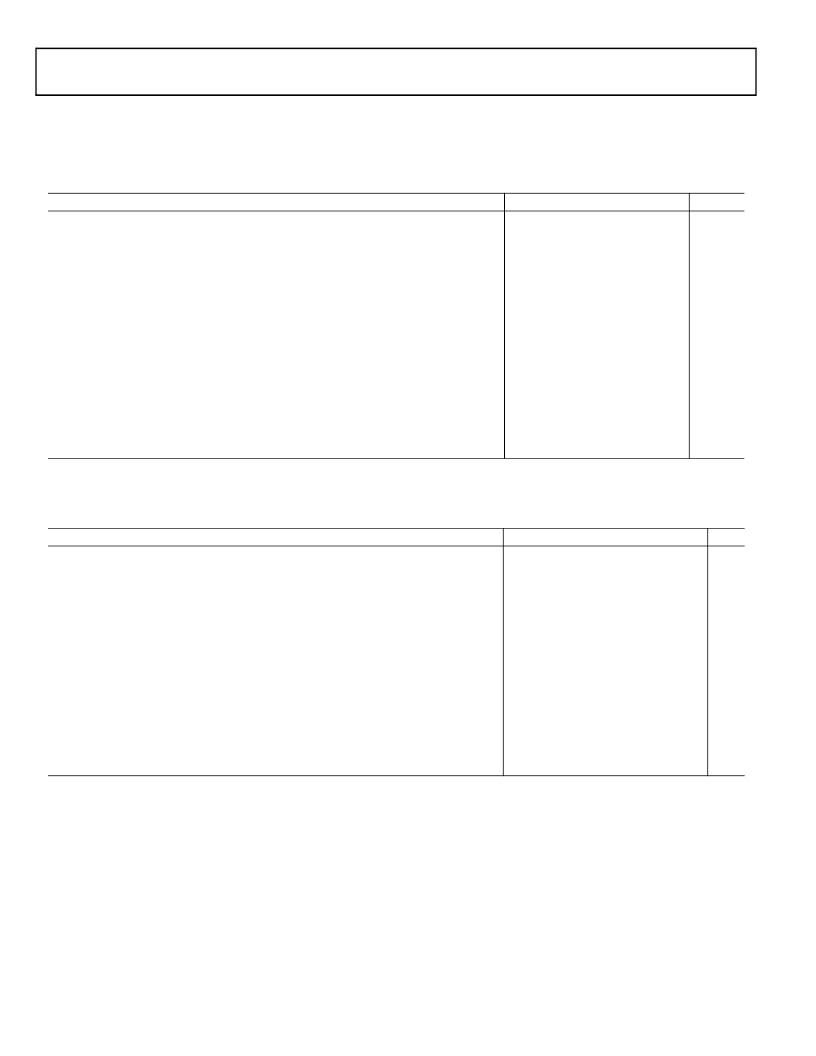

�Table� 24.� Serial� Ports—Internal� Clock�

�Parameter�

�Min�

�Max�

�Unit�

�Timing� Requirements�

�t� SFSI�

�t� HFSI�

�t� SDRI�

�t� HDRI�

�t� SCLKW�

�t� SCLK�

�TFSx/RFSx� Setup� Before� TSCLKx/RSCLKx� 1�

�TFSx/RFSx� Hold� After� TSCLKx/RSCLKx� 1�

�Receive� Data� Setup� Before� RSCLKx� 1�

�Receive� Data� Hold� After� RSCLKx� 1�

�TSCLKx/RSCLKx� Width�

�TSCLKx/RSCLKx� Period�

�8.0�

�–2.0�

�6.0�

�0.0�

�4.5�

�15.0�

�ns�

�ns�

�ns�

�ns�

�ns�

�ns�

�Switching� Characteristics�

�t� DFSI�

�t� HOFSI�

�t� DDTI�

�t� HDTI�

�t� SCLKIW�

�TFSx/RFSx� Delay� After� TSCLKx/RSCLKx� (Internally� Generated� TFSx/RFSx)� 2�

�TFSx/RFSx� Hold� After� TSCLKx/RSCLKx� (Internally� Generated� TFSx/RFSx)� 2�

�Transmit� Data� Delay� After� TSCLKx� 2�

�Transmit� Data� Hold� After� TSCLKx� 2�

�TSCLKx/RSCLKx� Width�

�–1.0�

�–2.0�

�4.5�

�3.0�

�3.0�

�ns�

�ns�

�ns�

�ns�

�ns�

�1�

�2�

�Referenced� to� sample� edge.�

�Referenced� to� drive� edge.�

�Rev.� E� |�

�Page� 32� of� 64� |�

�September� 2009�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ADZS-BF592-EZLITE

KIT EVAL EZ LITE ADZS-BF592

ADZS-BF609-EZBRD

KIT EVAL EZ-BOARD ADSP-BF60X

ADZS-HPUSB-ICE

TOOL EMULATOR USB HP CROSSCORE

ADZS-ICE-100B

EMULATOR BLACKFIN

AK-Y1301

CABLE SCSI-3 EXTENSION 68CONDUCT

AK-Y1303

CABLE SCSI-3 ADAPTER 50CONDUCTOR

AK-Y2301-R

CABLE SCSI II INT FLAT 68CON

AK-Y2310

CABLE SCSI-3 INTERNAL RAID FLAT

相关代理商/技术参数

ADZS-BF561-MMSKIT

功能描述:KIT STARTER MULTIMEDIA BF561 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Blackfin® 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF)

ADZS-BF561-MMSKIT

制造商:Analog Devices 功能描述:MEDIA KIT ((NW))

ADZS-BF592-EZLITE

功能描述:KIT EVAL EZ LITE ADZS-BF592 RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Blackfin® 产品培训模块:Blackfin® Processor Core Architecture Overview

Blackfin® Device Drivers

Blackfin® Optimizations for Performance and Power Consumption

Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA

ADZS-BF592-EZLITE

制造商:Analog Devices 功能描述:ADZS-BF592-EZLITE

ADZS-BF608-EZLITE

制造商:Analog Devices 功能描述:DIGITAL SIGNAL PROCESSOR - DEVELOPMENT TOOL

ADZS-BF609-EZBRD

功能描述:KIT EVAL EZ-BOARD ADSP-BF60X RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Blackfin® 产品培训模块:Blackfin® Processor Core Architecture Overview

Blackfin® Device Drivers

Blackfin® Optimizations for Performance and Power Consumption

Blackfin® System Services 特色产品:Blackfin? BF50x Series Processors 标准包装:1 系列:Blackfin® 类型:DSP 适用于相关产品:ADSP-BF548 所含物品:板,软件,4x4 键盘,光学拨轮,QVGA 触摸屏 LCD 和 40G 硬盘 配用:ADZS-BFBLUET-EZEXT-ND - EZ-EXTENDER DAUGHTERBOARDADZS-BFLLCD-EZEXT-ND - BOARD EXT LANDSCAP LCD INTERFACE 相关产品:ADSP-BF542BBCZ-4A-ND - IC DSP 16BIT 400MHZ 400CSBGAADSP-BF544MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF542KBCZ-6A-ND - IC DSP 16BIT 600MHZ 400CSBGAADSP-BF547MBBCZ-5M-ND - IC DSP 16BIT 533MHZ MDDR 400CBGAADSP-BF548BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF547BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF544BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGAADSP-BF542BBCZ-5A-ND - IC DSP 16BIT 533MHZ 400CSBGA

ADZS-BF609-EZLITE

功能描述:KIT EZ FOR BLACKFIN BF60X FAMILY RoHS:是 类别:编程器,开发系统 >> 通用嵌入式开发板和套件(MCU、DSP、FPGA、CPLD等) 系列:Blackfin® 标准包装:1 系列:PICDEM™ 类型:MCU 适用于相关产品:PIC10F206,PIC16F690,PIC16F819 所含物品:板,线缆,元件,CD,PICkit 编程器 产品目录页面:659 (CN2011-ZH PDF)

ADZS-BF706-EZMINI

功能描述:ADSP-BF70x EZ-KIT Mini? Blackfin? DSP Embedded Evaluation Board 制造商:analog devices inc. 系列:Blackfin? 零件状态:有效 板类型:评估平台 类型:DSP 核心处理器:- 操作系统:- 平台:EZ-KIT Mini? 配套使用产品/相关产品:ADSP-BF70x 安装类型:固定 内容:板,电缆,配件 标准包装:1